Sisukord:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:50.

- Viimati modifitseeritud 2025-01-23 14:40.

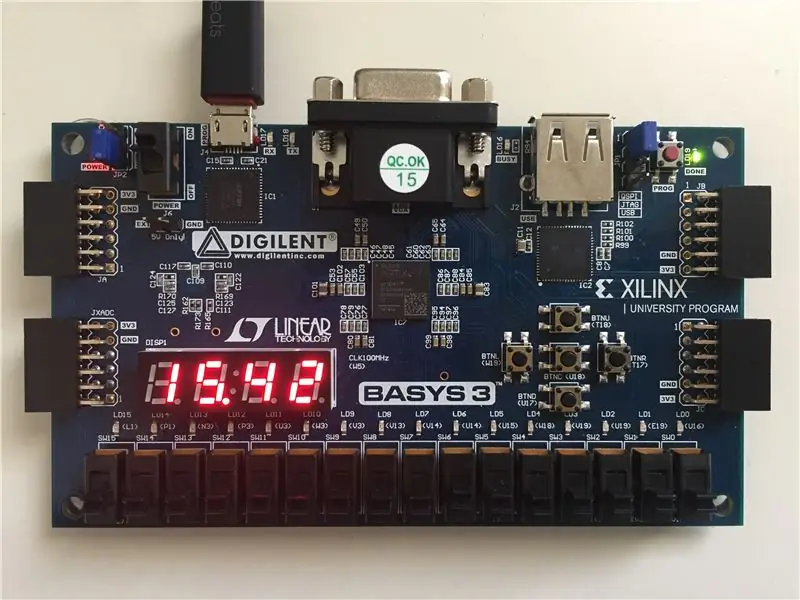

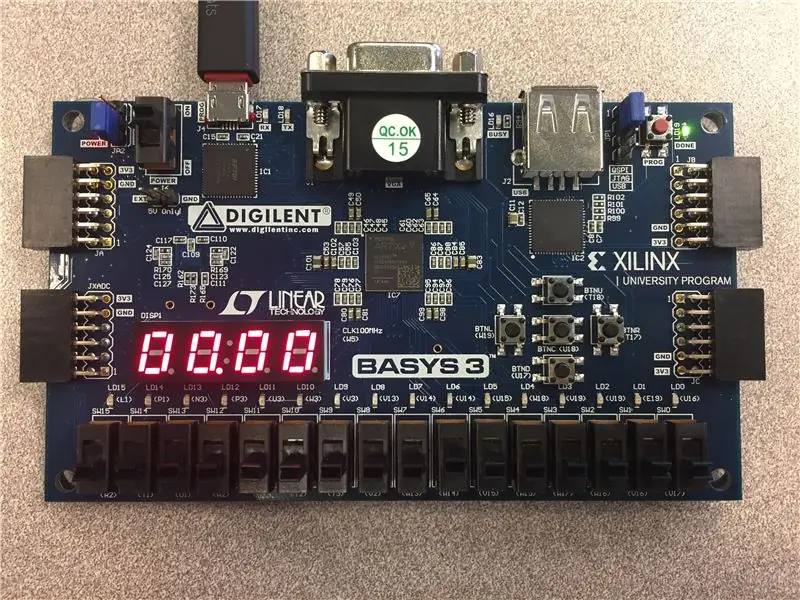

See on õpetus, kuidas teha stopperit, kasutades VHDL-i ja FPGA trükkplaati, näiteks Basys3 Atrix-7 plaati. Stopper suudab lugeda 00,00 sekundist 99,99 sekundini. See kasutab kahte nuppu, üks start/stopp -nupule ja teine lähtestusnupule. Numbrid kuvatakse tahvli seitsme segmendi ekraanil, kasutades selle anode ja katoode. Selle stopperi toimimiseks on vaja kolme erinevat faili.

Samm: riistvara/tarkvara

- Basys3 Atrix-7 FPGA plaat

- Vivado Design Suite firmalt Xilinx

- USB 2.0 A meessoost Micro-B isane

Samm: plokkskeem

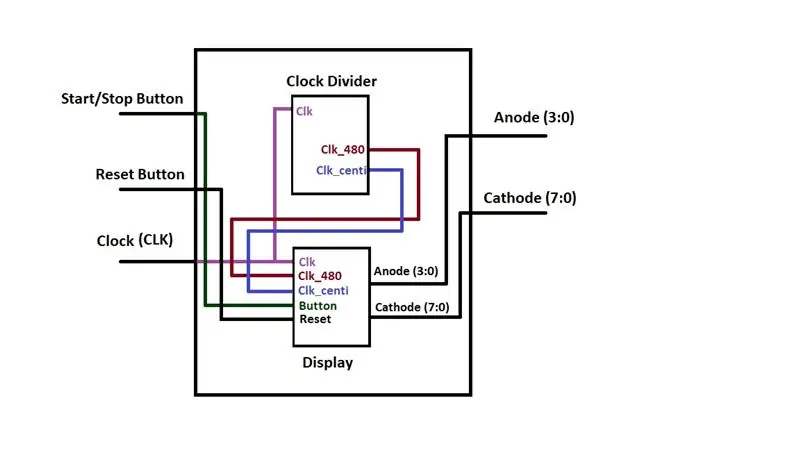

Üldisel stopperil on kolm sisendit ja kaks väljundit. Kolm sisendit on start/stop, reset ja clock. Start/stopp ja reset on nupud ja kell on plaadi 100MHz kell. Kaks väljundit on seitsme segmendi ekraani anoodid ja katoodid.

Esimesel moodulil (kellajaguril) on üks sisend ja kaks väljundit. Sisendiks on plaadi 100MHz kell ja väljundid on kaks eraldi kella, üks töötab 480Hz ja teine 0,5MHz.

Teisel moodulil (ekraanil) on viis sisendit ja kaks väljundit. Sisenditeks on plaadi 100MHz kell, kellajagurmooduli kaks kella ning start/stop ja reset nupud. Väljunditeks on anoodid ja katoodid.

Viimasel moodulil (modelleeritud kogu plokkskeemi järgi) on kolm sisendit ja kaks väljundit. See on fail, mis koondab kõik kokku. Sisendid on plaadi 100MHz ning start/stop ja reset nupud. Väljunditeks on anoodid ja katoodid, mis juhivad seitsme segmendi ekraani. Kõik sisendid ja väljundid on füüsiliselt lõppmooduli plaadil.

3. samm: olekdiagramm

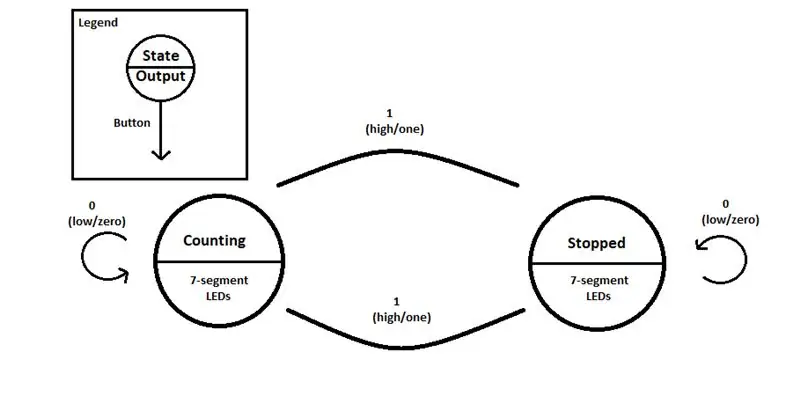

Ülaltoodud pilt näitab stopperi olekudiagrammi. Lähtestusnupu vajutamine ei mõjuta stopperi olekut. Järgmise oleku määrab start/stopp -nupp. Start/stopp on "HIGH", kui seda alla vajutatakse, kuid mitte siis, kui seda all hoitakse, ja "LOW", kui nupp on tagasi kerinud või pärast hetke "HIGH" all hoidmist all.

Kui stopper loeb ja käivitus-/seiskamisnupp läheb "HIGH", lõpetab see loendamise. Kui stopper on peatatud ja start/stopp -nupp läheb "HIGH", hakkab see uuesti loendama. Mõlema riigi puhul, kui käivitus-/seiskamisnupp on "LOW", jääb see olekusse, milles see praegu on.

4. samm: kellajaoturi moodul

Kellajaotusmoodulil on üks sisend, plaadi 100MHz kell ja kaks väljundit, 480Hz ja 0,5MHz kellad. 480Hz kella kasutatakse selleks, et kõik seitsme segmendi ekraanil olevad LED-id oleksid korraga sisse lülitatud, lülitades need neli kiiresti ümber. 0,5MHz kella kasutatakse selleks, et stopper loeks tegelikult sentsekundeid.

Samm: kuvamoodul

Sellel kuvarimoodulil on viis sisendit, tahvli 100MHz kell, kaks kella moodulist pärit kella ning start/stop ja reset nupud ning kaks väljundit, anoodid ja katoodid. Sellel moodulil on ka "loogika" selle kohta, kuidas stopper loeb ja sisaldab lõpliku oleku masinat.

6. samm: sidumismoodul

See viimane moodul ühendab ülejäänud kaks moodulit. Sellel on kolm sisendit, plaadi 100MHz kell ning start/stop ja reset nupud ning kaks väljundit, anoodid ja katoodid. 100MHz kell läheb kellajaotusmoodulile ja kuvamoodulile ning käivitus-/seiskamis- ja lähtestamisnupud kuvamoodulile. Kellajaotusmooduli väljundid (480Hz ja 0,5MHz) lähevad kuvarimooduli kahele kella sisendile. Kuvamooduli väljundid (anoodid ja katoodid) lähevad lõppmooduli väljunditesse.

7. samm: piirangud

Kaks sisendit võivad olla mis tahes nupud Basys3 Atrix-7 FPGA plaadil ja väljunditeks on neli anoodi ja kaheksa katoodi (kuna soovite ka kümnendkoha sekundite ja millisekundite vahel) seitsme segmendi ekraanil.

8. samm: valmis

Laadige programm üles oma Basys3 Atrix-7 FPGA-plaadile ja vajutage stopperi käivitamiseks nuppu Start/Stop!

Soovitan:

Põhiline stopper VHDL -i ja Basys3 -plaadi kasutamisel: 9 sammu

Põhiline stopper VHDL -i ja Basys3 -plaadi kasutamisel: Tere tulemast juhendisse, kuidas luua stopper, kasutades põhilist VHDL -i ja Basys 3 -tahvlit. Meil on hea meel teiega oma projekti jagada! See oli lõplik projekt CPE 133 (digitaalne disain) kursusel Cal Poly, SLO -s 2016. aasta sügisel

Arduino stopper: 4 sammu (piltidega)

Arduino stopper: see juhend annab teile teada, kuidas Arduino stopperit teha

Lihtne Arduino kell / stopper: 6 sammu (piltidega)

Lihtne Arduino kell / stopper: see " juhendatav " näitab ja õpetab teile, kuidas teha lihtsat Arduino Uno kella, mis toimib ka stopperina vaid mõne lihtsa sammuga

Stopper 30 m jooksuks (Arduino): 6 sammu (piltidega)

Stopper 30 m jooksuks (Arduino): see projekt tehti spetsiaalselt Soome pesapalli juhendamisel ja juunioride mängijate kiiruse testimisel 30 m jooksus. See arduino projekt oli ka minu õpingute kursus. Projektil olid tõusud ja mõõnad, kuid nüüd on see vähemalt toimiv

VHDL ühe minuti stopper: 5 sammu

VHDL -i üheminutiline stopper: see on õpetus, kuidas luua üheminutilist stopperit, kasutades VHDL -i ja Basys 3 -tahvlit. Selline seade sobib ideaalselt mängudeks, kus igal mängijal on oma käigu tegemiseks aega maksimaalselt üks minut. Stopper kuvab täpselt sekundeid ja millisekundeid