Sisukord:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:48.

- Viimati modifitseeritud 2025-01-23 14:40.

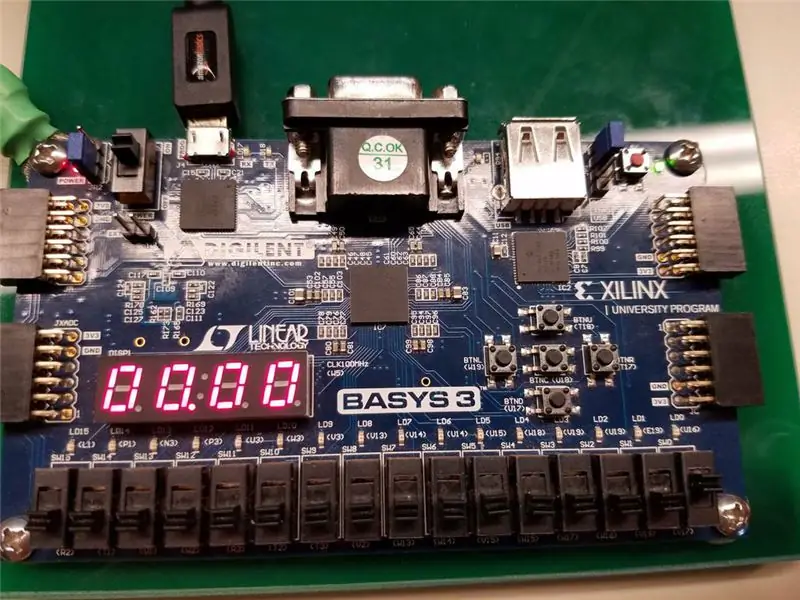

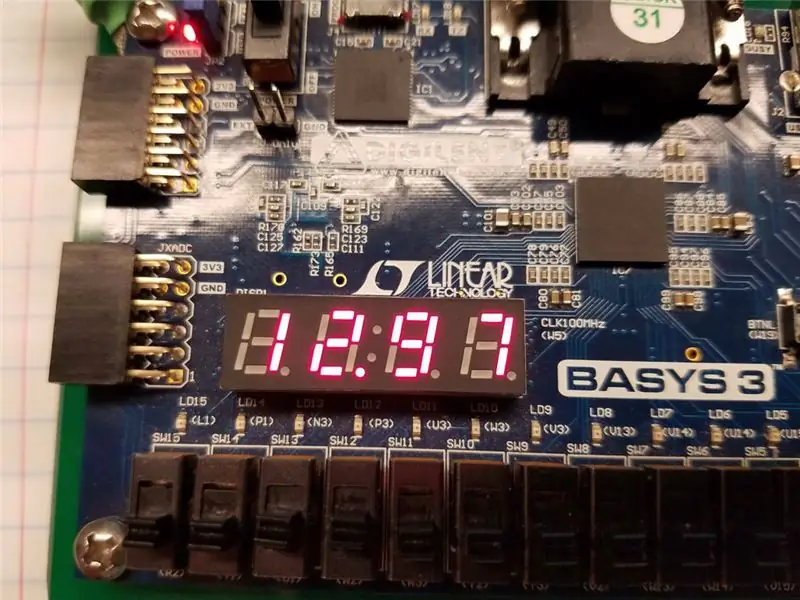

Tere tulemast juhendisse, kuidas luua stopperit, kasutades põhilist VHDL -i ja Basys 3 tahvlit. Meil on hea meel teiega oma projekti jagada! See oli 2016. aasta sügisel Cal Poly, SLO kursuse CPE 133 (digitaalne disain) viimane projekt. Meie ehitatud projekt on lihtne stopper, mis käivitab, lähtestab ja peatab aja. See võtab sisenditena kasutusele kolm Basys3 tahvlil olevat nuppu ja kellaaeg kuvatakse tahvli neljakohalise seitsme segmendi ekraanil. Möödunud aeg kuvatakse sekundite: sentsekundi vormingus. See kasutab tahvli süsteemikella sisendina, et jälgida kulunud aega ja väljastab aja seitsme segmendi ekraani neljakohalisele numbrile.

Samm: materjalid

Selle projekti jaoks vajalikud materjalid:

- 1 arvuti Xilinxist installitud Vivado Design Suite WebPackiga (eelista versiooni 2016.2)

- 1 Digilent Basys3 Xilinx Artix-7 FPGA plaat

- 1 USB -pordi kaabel

2. samm: sisendite ja väljundite seadistamine

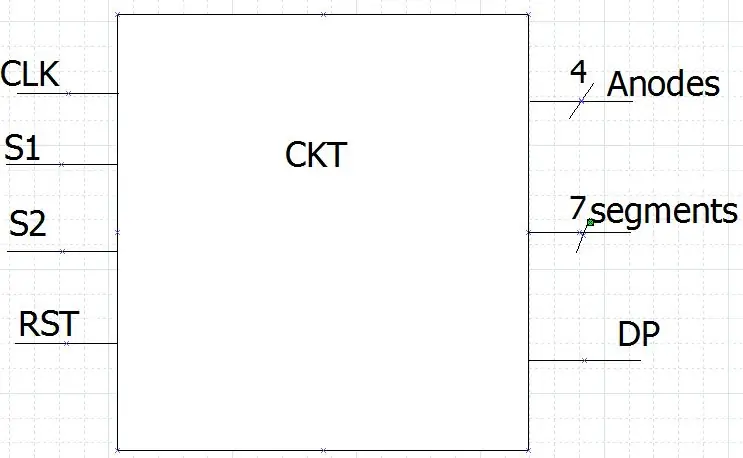

Ülaltoodud joonis näitab stopperi põhimooduli tipptasemel plokkskeemi. Stopper võtab sisendeid "CLK" (kell), "S1" (käivitusnupp), "S2" (pausi nupp) ja "RST" (lähtestamine) ning sellel on 4-bitine väljund "Anood", 7-bitine väljund "segment" ja ühebitine väljund "DP" (komakoht). Kui sisend "S1" on kõrge, hakkab stopper aega lugema. Kui "S2" on madal, peatab stopper aja. Kui "RST" on kõrge, peatub stopper ja lähtestab aja. Vooluahelas on neli alammoodulit: kellajagur, numbriloendur, seitsme segmendi kuvaridraiver ja seitsme segmendi ekraanikooder. Stopperi põhimoodul seob kõik alammoodulid kokku ning sisendite ja väljunditega.

3. samm: kellade valmistamine

Kellajaotusmoodul võtab süsteemikella sisse ja jagaja sisendi abil loob kella, mille kiirus ei ületa süsteemi kella kiirust. Stopper kasutab kahte erinevat kella moodulit, millest üks loob 500 Hz ja teine 100 Hz kella. Kellajaguri skemaatika on näidatud ülaltoodud joonisel. Kellajagur võtab sisse ühebitise sisendi "CLK", 32-bitise sisendi "jagaja" ja ühebitise väljundi "CLKOUT". "CLK" on süsteemi kell ja "CLKOUT" on saadud kell. Moodul sisaldab ka NOT väravat, mis lülitab signaali "CLKTOG", kui loendur jõuab jagaja väärtuseni.

Samm: loendage kümneni

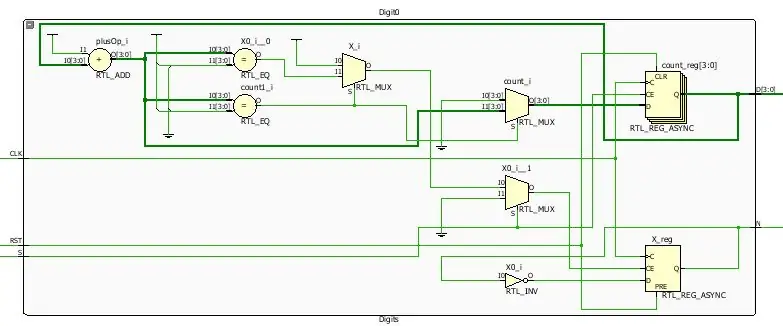

Numbriloendur loendab iga numbri vahemikus 0 kuni 10 ja loob järgmise kella, et järgmine number saaks sellest välja lülitada, kui arv jõuab kümneni. Moodul võtab sisse kolm ühebitilist sisendit "S", "RST" ja "CLK" "ja tulemuseks on ühebitine väljund" N "ja 4-bitine väljund" D ". Sisend "S" on sisendi lubamine. Kell lülitub sisse, kui "S" on kõrge, ja lülitub välja, kui "S" on madal. "RST" on lähtestussisend, nii et kell lähtestab, kui "RST" on kõrge. "CLK" on numbriloenduri kella sisend. "N" on kella väljund, millest saab järgmise numbri sisendkell. Väljund "D" esitab loenduri juures oleva numbri binaarväärtuse.

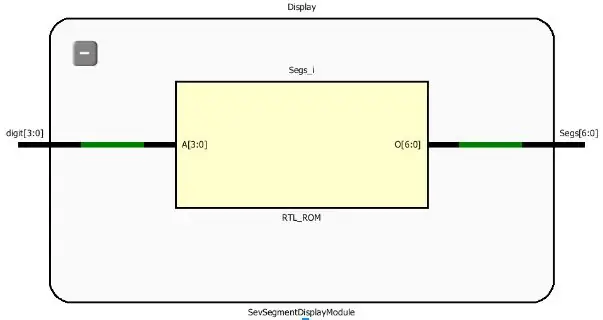

Samm: numbrite kuvamine

Seitsme segmendi kuvari kodeerija kodeerib seitsme segmendi kuvaridraiveri moodulilt saadud kahendnumbri ja muudab selle bittide vooks, mida tõlgendatakse kuvari iga segmendi väärtuseks „1” või „0”. Moodul võtab binaarnumbri vastu 4-bitise sisendina "numbrina" ja selle tulemuseks on 7-bitine väljund "segmendid". Moodul koosneb ühe juhtumiprotsessi plokist, mis määrab konkreetse 7-bitise voo igale võimalikule sisendväärtusele vahemikus 0 kuni 9. Iga seitsmebitise voo bitt kujutab endast ühte ekraanil olevate numbrite seitsmest segmendist. Segmendi järjekord voos on „abcdefg“, kusjuures „0“tähistab segmente, mis antud numbri jaoks helendavad.

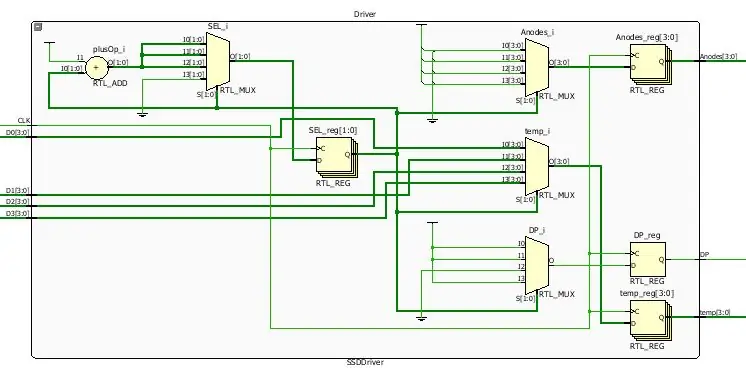

6. samm: stopperi kuvamine

Seitsme segmendi kuvaridraiveri moodulis on neli 4-bitist sisendit "D0", "D1", "D2" ja "D3", millest igaüks tähistab nelja kuvatavat numbrit. Sisend "CLK" on süsteemi kella sisend. Ühebitiline väljund "DP" tähistab seitsme segmendi ekraanil kümnendkohta. 4-bitine väljund "Anoodid" määrab, milline number seitsme segmendi ekraanil kuvatakse, ja 4-bitine väljund "temp" sõltub 2-bitise juhtsisendi "SEL" olekust. Moodul kasutab juhtsisendi "SEL" ja kolme väljundi jaoks 4 multiplekserit; "Anoodid", "temp" ja "DP".

7. samm: ühendage see kõik

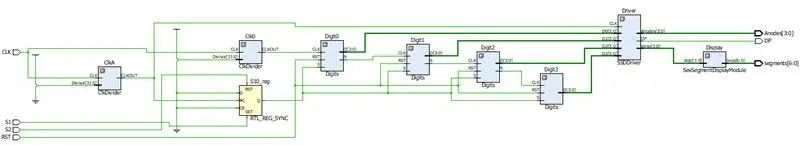

Käivitus- ja pausinuppude loomiseks kasutatakse 500 Hz kellast välja jooksvat protsessiplokki „if”. Seejärel ühendage kõik alammoodulid stopperi peamoodulis kokku, deklareerides iga üksiku alammooduli komponendid ja kasutades erinevaid signaale. Numbrilised alammoodulid võtavad vastu eelmise numbri alammooduli taktsignaali ja esimene võtab vastu 100 Hz kella. Seejärel muutuvad numbriliste alammoodulite "D" väljundid seitsme segmendi kuvaridraiveri mooduli "D" sisenditeks. Ja lõpuks muutub seitsme segmendi kuvaridraiveri mooduli väljund "temp" seitsme segmendi kodeerimismooduli "temp" sisendiks.

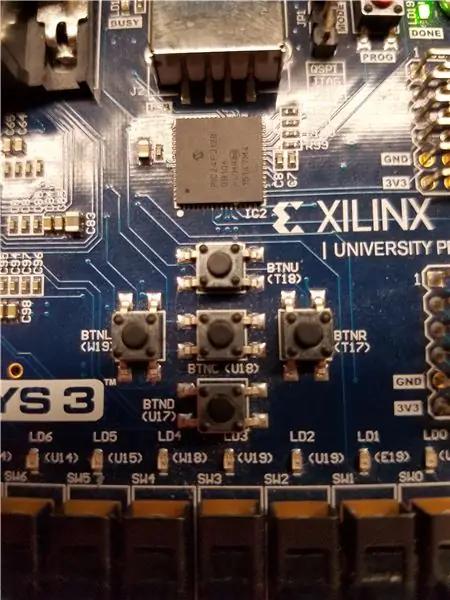

8. samm: piirangud

Sisendite "RST", "S1" ja "S2" jaoks kasutage kolme vajutusnuppu (W19, T17 ja U18). W19 on lähtestamisnupp, T17 on käivitusnupp (S1) ja U18 on pausinupp (S2). Pordi W5 abil on vaja piirata ka kella sisendi sisendit. Samuti pidage meeles, et lisage see rida kella piirangule:

create_clock -add -name sys_clk_pin -periood 10.00 -waveform {0 5} [get_ports {CLK}]

Samuti ühendage anoodid ja segmendid tahvliga, nii et stopper kuvatakse seitsme segmendi ekraanil, nagu on näha piirangute failis.

9. samm: testimine

Veenduge, et teie seade töötab, mängides kolme nupuga: vajutage ja hoidke neid all igas võimalikus järjekorras, et leida võimalikke probleeme oma koodiga.

Soovitan:

HC-05 (bluetooth) Koduautomaatika moodul Põhiline: 3 sammu

HC-05 (bluetooth) Koduautomaatika moodul Põhiline: oma viimases projektis kontrollisin LED-i nupuvajutusega, kuid selles projektis asendasin PUSH BUTTON-i HC-05 mooduliga. Soovitan tungivalt need projektid enne läbi vaadata selle projektiga jätkates. Kõik üksikasjad leiate siit

Kordiline algoritm VHDL -i kasutamisel: 4 sammu

Kordialgoritm VHDL -i abil: ## See on Google'i kõige enam klõpsatud link CORDIC ALGORITHM -i VHDL -i rakendamiseks siinus- ja koosinuslaine tekitamiseks ## Praegu on olemas palju riistvaratõhusaid algoritme, kuid need pole hästi teada pehme sõja domineerimine

VHDL Basys3: Connect 4 Mäng: 5 sammu

VHDL Basys3: Connect 4 mäng: Sissejuhatus: See on Connect 4 digitaalne loogikamäng, mis on loodud VHDL -is, kasutades tarkvara Vivado ja programmeeritud Basys3 -tahvlile. Selle projekti ülesehitus ja disain on vahepealsed, kuid uustulnukad saavad samme kopeerida ja luua digitaalse

VHDL ühe minuti stopper: 5 sammu

VHDL -i üheminutiline stopper: see on õpetus, kuidas luua üheminutilist stopperit, kasutades VHDL -i ja Basys 3 -tahvlit. Selline seade sobib ideaalselt mängudeks, kus igal mängijal on oma käigu tegemiseks aega maksimaalselt üks minut. Stopper kuvab täpselt sekundeid ja millisekundeid

VHDL stopper: 8 sammu (piltidega)

VHDL stopper: see on õpetus stopperi valmistamiseks, kasutades VHDL-i ja FPGA trükkplaati, näiteks Basys3 Atrix-7 plaati. Stopper suudab lugeda 00,00 sekundist 99,99 sekundini. See kasutab kahte nuppu, üks start/stopp -nupule ja teine