Sisukord:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:46.

- Viimati modifitseeritud 2025-01-23 14:40.

Autor: AmCoderhttps://www.linkedin.com/in/mitu

Teave: Mitu Raj - lihtsalt hobbyst ja õppija - kiibidisainer - tarkvaraarendaja - füüsika ja matemaatika entusiast Lisateave AmCoderi kohta »

## See on Google'i kõige enam klõpsatud link CORDIC ALGORITHMi VHDL -i rakendamiseks siinus- ja koosinuslaine tekitamiseks ## Praegu on olemas palju riistvara tõhusaid algoritme, kuid need pole tarkvarasüsteemide domineerimise tõttu hästi teada. palju aastaid. CORDIC on selline algoritm, mis pole midagi muud kui nihke- ja lisaloogika, mida kasutatakse mitmesuguste funktsioonide, sealhulgas teatud trigonomeetriliste, hüperboolsete, lineaarsete ja logaritmiliste funktsioonide arvutamiseks. Seda algoritmi kasutatakse kalkulaatorites jne. Seega, kasutades lihtsaid käiguvahetajaid ja liitureid, saame kordilise algoritmi abil kujundada riistvara, mille keerukus on väiksem, kuid DSP võimsus. Seetõttu saab selle VHDL -is või Verilogis kujundada palja RTL -kujundusena, ilma spetsiaalseid ujukomaüksusi või keerukaid matemaatilisi IP -sid kasutamata.

Samm: VHDL ja Modelsim

Siin rakendatakse kordilist algoritmi VHDL abil siinus- ja kooselaine genereerimiseks. See suudab sisendnurga siinust ja koosinusust väga täpselt väljastada. Kood on sünteesitav FPGA -l. Modelsimit kasutatakse disaini ja katsestendi simuleerimiseks.

2. etapp: disaini ja katsestendi VHDL -kood

Ujukomaarvude esitamiseks kasutatakse binaarset skaleerimistehnikat.

Enne kodeerimist lugege lisatud dokumente.

Mine läbi simuleerides cordic_v4.vhd - disain - sisend on nurk 32 bitti + märgi bit; see võib töödelda mis tahes nurka 0 kuni +/- 360 kraadi sisendi täpsusega 0,000000000233 kraadi. Sisendi andmisel -> MSB on märgibitt ja ülejäänud 32 bitti tähistavad suurusjärku. täpsusega 0,00001526. Pange tähele, et väljund kuvatakse 2 komplimendi kujul, kui vastav siinus- või cos -väärtus on negatiivne. Testb.vhd simuleerimine - disainilahenduse testpink (1) Sisendnurgad ja tõmbe lähtestamine = '0'. Pärast kahte simuleerimisetappi tõmmake "1" ja "käivitage kõik". (2) Seadistage simulatsiooniaknas sin ja cos signaalide raadius kümnendkohaks ja vorming> Analoog (automaatne). (3) Lainekuju nägemiseks vähendage korralikult.

3. samm: manustatud failid

(1) cordic_v4.vhd - disain. (2) testb.vhd - disainilahenduse katsestend.

(3) Dokument selle kohta, kuidas nurga sisendeid sundida ja kahendtulemusi teisendada.

Värskendus: need failid on ebakindlad ja neid ei pakuta enam. PALUN KASUTAGE FILE JÄRGMISEST SAMMUST

Samm 4: Mini -Cordic IP Core - 16 -bitine

Ülaltoodud rakenduse piirang on aeglane, madalam taktsagedus, kuna arvutused tehakse ühe taktsükli jooksul. Mini-Cordic IP Core- 16 bit

- Kriitilised teed, mis on jõudluse parandamiseks jaotatud mitmele tsüklile.- Kiirem- FPGA tõestatud disain sünteesitud kuni 100 Mhz kellani.- Suurem ala optimeeritud HDL-i abil, väiksem riistvara.- Lisatud laadimis- ja valmisolekusignaalid.- Ainus miinus on väiksem eraldusvõime võrreldes eelmine. Testpink:

täielikult automatiseeritud 0 kuni 360 kraadise nurga all

Manustatud failid: 1) mini -cordic peamine vhdl -fail 2) mini -juhtpaneeli testpink 3) Mini -Cordic IP -tuuma käsiraamat 4) Dokumendid nurkade sundimiseks ja tulemuste teisendamiseks

Kõigi küsimuste korral võtke minuga julgelt ühendust:

Mitu Raj

jälgi mind:

post: iammituraj@gmail.com

### Allalaadimisi kokku: 325 seisuga 01.05.2021 ###

### Koodi viimati muudetud: juuli-07-2020 ###

Soovitan:

DINO MÄNG LDR -i KASUTAMISEL: 5 sammu

DINOMÄNG, KASUTATUD LDR-i: Dinosauruste mäng, tuntud ka kui T-Rex Game ja Dino Runner, on sisseehitatud brauserimäng Google Chrome'i veebibrauseris. Mängu lõi Sebastien Gabriel 2014. aastal ja sellele pääseb juurde, kui vajutate Google Chrome'is võrguühenduseta tühikut. L

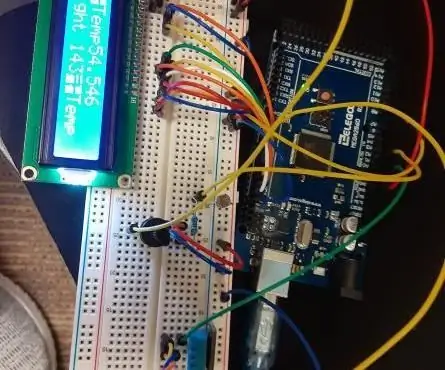

Takistus vältides robotit Arduino Nano kasutamisel: 5 sammu

Takistus roboti vältimiseks Arduino Nano abil: Selles juhendis kirjeldan, kuidas saate teha takistuse, vältides Arduino abil robotit

Lauamäng Tehisintellekt: Minimaxi algoritm: 8 sammu

Lauamäng Tehisintellekt: Minimaxi algoritm: kas olete kunagi mõelnud, kuidas arvutid, mille vastu males või kabes mängite, on tehtud? Ärge otsige sellest juhendist kaugemale, sest see näitab teile, kuidas luua minimaalset maksimumalgoritmi kasutades lihtsat, kuid tõhusat tehisintellekti (AI)! Kasutades th

Põhiline stopper VHDL -i ja Basys3 -plaadi kasutamisel: 9 sammu

Põhiline stopper VHDL -i ja Basys3 -plaadi kasutamisel: Tere tulemast juhendisse, kuidas luua stopper, kasutades põhilist VHDL -i ja Basys 3 -tahvlit. Meil on hea meel teiega oma projekti jagada! See oli lõplik projekt CPE 133 (digitaalne disain) kursusel Cal Poly, SLO -s 2016. aasta sügisel

Tic Tac Toe Arduino'l koos AI -ga (Minimaxi algoritm): 3 sammu

Tic Tac Toe Arduino'l koos AI -ga (Minimaxi algoritm): Selles juhendis näitan teile, kuidas ehitada Tic Tac Toe mängu AI abil Arduino abil. Võite mängida Arduino vastu või vaadata, kuidas Arduino enda vastu mängib. Ma kasutan algoritmi nimega "minimax algoritm"