Sisukord:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:49.

- Viimati modifitseeritud 2025-01-23 14:40.

Selle projekti eesmärk on luua nutika peegli kujutise kuvamise funktsionaalsus. Peegel suudab kuvada prognoose (päikesepaisteline, osaliselt päikeseline, pilvine, tuuline, vihm, äike ja lumi) ja temperatuuri väärtusi vahemikus -9999 ° kuni 9999 °. Prognoosi- ja temperatuuriväärtused on kõvasti kodeeritud, justkui jäljendades neid ilma API -st parsimisel.

Projekt kasutab Zynq-Zybo-7000 tahvlit, mis töötab FreeRTOS-iga ning kasutab riistvara kujundamiseks ja programmeerimiseks Vivado 2018.2.

Osad:

Zynq-Zybo-7000 (koos FreeRTOS-iga)

19 LCD (640x480)

VGA kaabel

12 "x 18" akrüülpeegel

Samm: Vivado seadistamine

Laadige Xilinxist alla Vivado 2018.2 ja kasutage Webpacki litsentsi. Käivitage Vivado ja "Loo uus projekt" ning pange sellele nimi. Järgmisena valige "RTL Project" ja märkige "Ära täpsusta allikaid praegu." Osa valimisel valige "xc7z010clg400-1" ja vajutage järgmisel lehel nuppu "Lõpeta".

2. samm: VGA draiveri IP pakkimine

Lisage kujundusallikatesse fail vga_driver.sv. Seejärel klõpsake "Tööriistad" ja valige "Loo ja pakkige uus IP". Valige "Pakkige oma praegune projekt". Seejärel valige IP -asukoht ja "Kaasa.xci -failid". Klõpsake hüpikaknas nuppu "OK" ja seejärel nuppu "Lõpeta".

Minge jaotises „Pakendamisetapid” jaotisse „Ülevaatus ja pakett” ning valige „Paketi IP”.

Nüüd peaks vga_driver olema IP -blokeeringuna saadaval.

Samm: Zynq IP

Jaotises "IP -integreerija" valige "Loo ploki kujundus". Lisage "ZYNQ7 Processing System" ja topeltklõpsake plokki. Klõpsake "Impordi XPS -i seaded" ja laadige üles fail ZYBO_zynq_def.xml.

Seejärel avage jaotises "PS-PL Configuration" rippmenüü "AXI Non Secure Enablement" ja märkige "M AXI GP0 interface".

Seejärel avage jaotises "MIO Configuration" rippmenüü "Application Processor Unit" ja märkige "Timer 0" ja "Watchdog".

Lõpuks avage jaotises "Kella seadistamine" rippmenüü "PL Fabric Clocks" ja kontrollige "FCLK_CLK0" ja 100 MHz juures.

Samm: GPIO IP

Lisage ploki kujundusele kaks GPIO plokki. GPIO -sid kasutatakse piksliaadressi ja pikslite RGB -komponentide juhtimiseks. Seadistage plokid, nagu ülaltoodud piltidel näidatud. Kui olete mõlemad plokid lisanud ja konfigureerinud, klõpsake nuppu "Käivita ühenduse automatiseerimine".

GPIO 0 - kanal 1 juhib piksliaadressi ja kanal 2 punast värvi.

GPIO 1 - kanal 1 juhib rohelist värvi ja kanal 2 sinist.

Samm: blokeerige mälu

Lisage plokkide kujundusele plokkmälu generaatori IP ja konfigureerige, nagu ülal näidatud. Pikslivärvid kirjutatakse mäluaadressidele, mida VGA draiver loeb. Aadressirida peab vastama kasutatavate pikslite arvule, seega peab see olema 16 bitti. Andmed on samuti 16 bitti, kuna seal on 16 värvibitti. Me ei hooli ühegi tunnustusbiti lugemisest.

6. samm: muu IP

Lisatud pdf -il on näidatud valminud plokidisain. Lisage puuduv IP ja lõpetage ühendused. Samuti "Make Externals" VGA värviväljundite ning vertikaalse ja horisontaalse sünkroonimise väljundite jaoks.

xlconcat_0 - ühendab üksikud värvid, moodustades ühe 16 -bitise RGB -signaali, mis sisestatakse Block RAM -i.

xlconcat_1 - ühendab VGA draiveri veergude ja ridade signaalid ning suunatakse ploki RAM porti B. See võimaldab VGA draiveril lugeda pikslite värviväärtusi.

VDD - Constant HIGH on ühendatud Block RAM -i kirjutamisvõimalusega, nii et meil on alati õigus sellele juurde pääseda.

xlslice_0, 1, 2 - viilusid kasutatakse RGB -signaali jagamiseks üksikuteks R-, G- ja B -signaalideks, mida saab VGA draiverisse sisestada.

Kui ploki kujundus on lõpule jõudnud, looge HDL -ümbris ja lisage piirangute fail.

*Plokidisain põhineb Benlin1994 kirjutatud õpetusel*

7. toiming: SDK

Selle ploki kujunduse käitamise kood on toodud allpool. Init.c sisaldab joonistust käsitlevaid funktsioone (prognoosid, numbrid, kraadisümbol jne). Main.c peamine silmus käivitatakse, kui plaat on programmeeritud. See tsükkel määrab prognoosi ja temperatuuri väärtused ning kutsub seejärel käivitusfunktsioonid sisse init.c. See vaatab praegu läbi kõik seitse prognoosi ja kuvab neid üksteise järel. Soovitatav on lisada murdepunkt reale 239, et saaksite näha iga pilti. Kood on kommenteeritud ja annab teile rohkem teavet.

8. samm: järeldus

Praeguse projekti täiustamiseks võiks üles laadida eellaaditud ennustuspildid COE -failide kujul mälugeneraatorite blokeerimiseks. Nii et selle asemel, et prognoose käsitsi joonistada, nagu tegime C -koodis, võiks lasta pildid sisse lugeda. Proovisime seda teha, kuid ei saanud seda tööle. Suutsime piksliväärtusi lugeda ja neid väljastada, kuid see lõi räpaseid pilte, mis ei sarnanenud RAM -i laaditud piltidega. Block Memory Generator andmeleht on kasulik lugeda.

Projekt on sisuliselt pool nutikat peeglit, kuna sellel puudub Interneti -ühenduse aspekt. Selle lisamine annaks täieliku nutika peegli.

Soovitan:

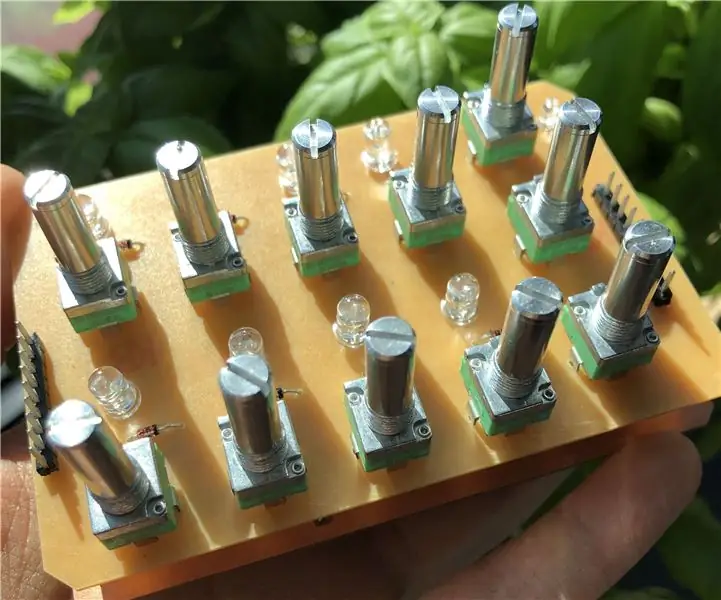

Atari punkkonsool beebiga 8 sammu järjestus: 7 sammu (piltidega)

Atari punkkonsool koos beebi 8-astmelise sekveneerijaga: see vaheehitus on kõik-ühes Atari punk-konsool ja beebi 8-astmeline järjestus, mida saate freesida Bantam Tools töölaua PCB-freespingis. See koosneb kahest trükkplaadist: üks on kasutajaliidese (UI) plaat ja teine on utiliit

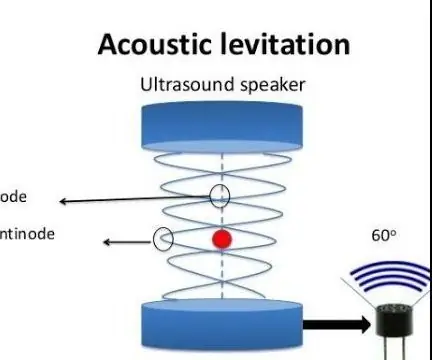

Akustiline levitatsioon Arduino Unoga samm-sammult (8 sammu): 8 sammu

Akustiline levitatsioon Arduino Uno abil samm-sammult (8 sammu): ultraheliheli muundurid L298N DC-naissoost adapteri toiteallikas isase alalisvoolupistikuga Arduino UNOBreadboard ja analoogpordid koodi teisendamiseks (C ++)

4G/5G HD -video otseülekanne DJI droonilt madala latentsusega [3 sammu]: 3 sammu

![4G/5G HD -video otseülekanne DJI droonilt madala latentsusega [3 sammu]: 3 sammu 4G/5G HD -video otseülekanne DJI droonilt madala latentsusega [3 sammu]: 3 sammu](https://i.howwhatproduce.com/images/009/image-25904-j.webp)

4G/5G HD-video otseülekanne DJI droonilt madala latentsusega [3 sammu]: Järgnev juhend aitab teil saada HD-kvaliteediga otseülekandeid peaaegu igalt DJI droonilt. FlytOSi mobiilirakenduse ja veebirakenduse FlytNow abil saate alustada drooni video voogesitust

Polt - DIY juhtmeta laadimise öökell (6 sammu): 6 sammu (piltidega)

Bolt - DIY juhtmeta laadimise öökell (6 sammu): Induktiivsed laadimised (tuntud ka kui juhtmeta laadimine või juhtmeta laadimine) on traadita jõuülekande tüüp. See kasutab kaasaskantavatele seadmetele elektrit pakkumiseks elektromagnetilist induktsiooni. Kõige tavalisem rakendus on Qi traadita laadimisst

4 sammu aku sisemise takistuse mõõtmiseks: 4 sammu

4 sammu aku sisemise takistuse mõõtmiseks: Siin on 4 lihtsat sammu, mis aitavad mõõta taigna sisemist takistust