Sisukord:

- Samm: PWM-mooduli lähtefaili loomine

- 2. samm: PWM-mooduli loomine- Vivado häälestus

- 3. samm: PWM-mooduli loomine- looge projektifail

- Samm 4: PWM-mooduli loomine- plokkide kujundus ja piirangute seadistus (I)

- 5. samm: PWM-mooduli loomine- plokkide kujundus ja piirangute seadistus (II)

- 6. etapp: PWM-mooduli loomine- plokkide kavandamine ja piirangute seadistamine (III)

- Samm 7: PWM-mooduli ehitamine- plokkide kavandamine ja piirangute seadistamine (IV)

- 8. samm: PWM-mooduli loomine- plokkide kujundus ja piirangute seadistus (V)

- 9. samm: PWM-mooduli ehitamine- riistvara installimine

- 10. samm: PWM-mooduli loomine- looge bitivoo ja käivitage SDK

- 11. samm: PWM-mooduli loomine- looge Xilinxi SDK-s uus rakendus

- 12. samm: PWM-mooduli loomine- ülevaade Project Explorerist (I)

- 13. samm: PWM-mooduli loomine- ülevaade Project Explorerist (II)

- 14. samm: PWM-mooduli loomine- ülevaade Project Explorerist (III)

- Samm 15: PWM-mooduli loomine- PWM-funktsiooni mähis (I)

- 16. etapp: PWM-mooduli loomine- PWM-funktsiooni pakkimine (II)

- 17. etapp: PWM-mooduli loomine- PWM-funktsiooni pakkimine (III)

- 18. samm: PWM-mooduli ehitamine- käivitage see

- 19. samm: videotöötluse voogesitus Digilent ZYBO -s OV7670 abil

- Samm: täitke plokkskeem

- Samm: ühendage OV7670 ZYBO -ga

- 22. samm: looge plokkide kujundus

- 23. toiming: lisage VHDL -failid OV7670 kaamera juhtimiseks ja jäädvustamiseks

- Samm: lisage piirangute fail

- Samm: lisage HLS IP jaoks IP Repo

- Samm: lisage moodulid ja IP

- Samm 27: IP -konfiguratsiooniseaded

- Samm: lisage ja konfigureerige PS IP -blokeering

- Samm 29: 1. osa. PWM -mooduli ehitamine servomootoritele

- 30. samm: videosisendi külgühendused (esile tõstetud)

- Samm: ühendused OV7670 -ga

- Samm 32: Ühendused video väljundis

- Samm 33: käivitage plokkide ja ühenduse automatiseerimine

- Samm: looge HDL -pakend

- Samm: looge bitivoo, eksportige riistvara SDK -sse, käivitage SDK Vivadost

- 36. samm: SDK (FreeRTOS puudub)

- 37. samm: FreeRTOS -i juurutamine

- Samm 38: Kasutusjuhised

- Samm 39: Viited ja lingid

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:50.

- Viimati modifitseeritud 2025-01-23 14:40.

Alustage esimesest sammust, et saada teavet 2-teljelise servo PWM-kontrolleri loomise kohta.

Alustage kogu projekti ulatuslikust plokkskeemist (samm 19).

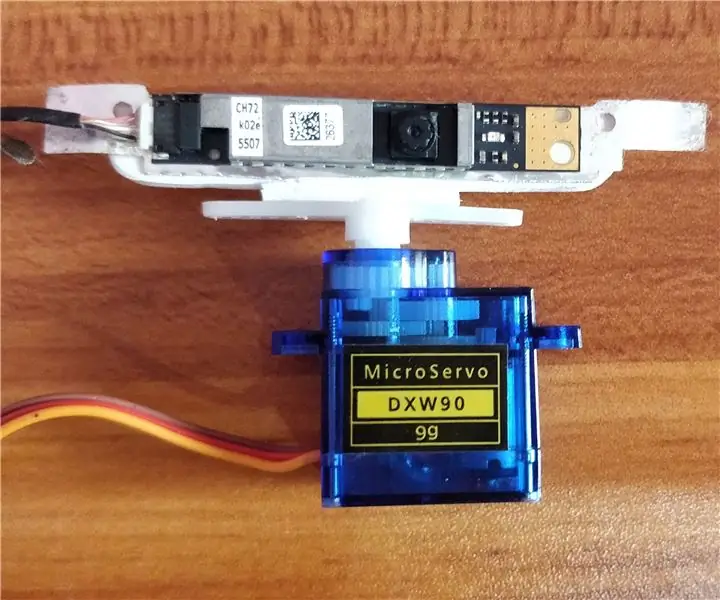

Kaamera + panoraami/kallutamise seadistus, mida kasutasime:

Servode ühendamiseks kasutati Digilent'i PmodCON3.

Samm: PWM-mooduli lähtefaili loomine

2. samm: PWM-mooduli loomine- Vivado häälestus

Esiteks laadige Xilinxi veebisaidilt alla Vivado Design Suite. Installige kogu disainikomplekt, sealhulgas Vivado tarkvaraarenduskomplekt (SDK). See projekt kasutab versiooni 2017.2.

Vahepeal tuleks Digilent Adept 2 installida ka Zybo plaadi draiveriks.

3. samm: PWM-mooduli loomine- looge projektifail

Enne projektifaili loomist veenduge, et olete siin juba õpetuseks Zybo faili õigesti installinud:

Vivado versioon 2015.1 ja uuemad tahvelfailide installimine

Avage Vivado 2017.2. Klõpsake kiirkäivitusel nuppu Loo projekt -> Järgmine -> Projekti nimi (nimetage siin oma projekti nimi) -> Projekti tüüp. Valige projekti tüübist RTL -projekt ja märkige ruut „Ärge määrake allikaid praegu”. Seejärel valige vaikeosa jaoks kuvatavaks nimeks „Lauad” ja „Zybo”. Seejärel klõpsake projekti alustamiseks nuppu Lõpeta.

Samm 4: PWM-mooduli loomine- plokkide kujundus ja piirangute seadistus (I)

Klõpsake Flow Navigatoris nuppu "" Loo ploki kujundus "ja vajutage nuppu OK. vajalike IP -de lisamiseks klõpsake "+" märki. Lisama:

- Üks ZYNQ7 töötlussüsteem Kaks AXI taimerit

- Kaks AXI taimerit

5. samm: PWM-mooduli loomine- plokkide kujundus ja piirangute seadistus (II)

Pärast IP -de lisamist käivitage plokkide automatiseerimine ja ühenduse automatiseerimine. Kui automatiseerimine on lõpule viidud, paremklõpsake plokil “axi_timer_0” nuppu pwm0 -> Tee väline. Pange välisele tihvtile pwm0 nimi pwm_Xaxis. Samuti korrake ülaltoodud protsessi plokil „axi_timer_1” ja nimetage pwm0 väline tihvt pwm_Zaxis.

6. etapp: PWM-mooduli loomine- plokkide kavandamine ja piirangute seadistamine (III)

Pange tähele, et iga kord, kui lõpetame plokkide kujundamise Vivados, peame looma HDL -ümbrise. Kuna see on iga projekti tipptasemel moodul.

Samm 7: PWM-mooduli ehitamine- plokkide kavandamine ja piirangute seadistamine (IV)

Nüüd peame seadistama oma piirangute faili, et määrata meie plokkskeemiga ühendatud tihvtid. Sulgege aken Blokeeri kujundus, vahekaardil Allikad, „Lisa allikaid”-> Lisage või looge piiranguid-> lisage Zybo-Master.xdc meie piirangute failidena.

8. samm: PWM-mooduli loomine- plokkide kujundus ja piirangute seadistus (V)

Avage piirangute fail Zybo-Master.xdc kaustast Piirangud, tühistage pordid, mida soovime väljundsignaalidena määrata, ja nimetage ümber „get_ports {XXXX}”, mis tähistab plokkskeemil nimetatud välist tihvti. Piirangute faili seadistus on näidatud joonisel.

9. samm: PWM-mooduli ehitamine- riistvara installimine

Ühendage servomootorid seadmega Pmod CON3. TowerPro SG90 on selles projektis kasutatud servomootori mudel. Servomootori juhtmete puhul tähistab oranž juhe PWM -signaali, mis on ühendatud PIG CON3 SIG -tihvtiga. Punane juhe Vcc on toitejuhe, mis on ühendatud VS -pistikuga Pmod CON3 -s. Lõpuks on pruun traat Gnd maandusjuhe, mis on ühendatud GND tihvtiga. Seejärel sisestage Pmod CON3 Zybo Boardi JD -pordi ülemisele reale.

10. samm: PWM-mooduli loomine- looge bitivoo ja käivitage SDK

1. Käivitage vahekaardil Project Navigator käsk Generate BitStream.

2. Riistvara eksport: Fail> Eksport> Ekspordi riistvara-> märkige ruut „kaasata bitivool”-> OK 3. Käivitage SDK: Fail-> Käivitage SDK.

11. samm: PWM-mooduli loomine- looge Xilinxi SDK-s uus rakendus

Looge uus rakendus:

Fail> Uus> Rakendusprojekt -> Sisestage oma projekti nimi -> Lõpeta

Project Exploreri all peaks olema kolm kausta.

Sel juhul on „design_1_wrapper_hw_platform_0” Vivado varem eksporditud kaust. Axis_2_PWM_SDK_bsp on plaadi tugipaketi kaust. Ja Axis_2_PWM_SDK on meie peamine projekti kaust SDK -s. Faili „helloworld.c” näete Axis_2_PWM_SDK kausta „src” all, kus põhifail on „helloworld.c”.

12. samm: PWM-mooduli loomine- ülevaade Project Explorerist (I)

Kontrollime mõningaid faile Project Exploreris. Esiteks avage kaustas „design_1_wrapper_hw_platform_0” kaust „system.hdf”. See fail näitab protsessori ps7_cortex9 aadressikaarti ja meie disainis olevaid IP -plokke.

13. samm: PWM-mooduli loomine- ülevaade Project Explorerist (II)

Seejärel kontrollige kausta „Axis_2_PWM_SDK_bsp” all olevaid faile „include” ja „libsrc”. Siin olevad raamatukogufailid võimaldavad meil suhelda riistvara välisseadmetega ilma registreid "mängimata".

14. samm: PWM-mooduli loomine- ülevaade Project Explorerist (III)

BSP dokumentatsiooni kaudu leitakse xtmrctr.h AXI taimeriga seotud Xilinxi taimerijuhtimisteegina. Tavaliselt leiame siit soovitud PWM -funktsiooni. Kui aga loete dokumentatsiooni „tmrctr_v4_3”, näitab see, et draiver ei toeta praegu seadme PWM -toimingut. PWM -funktsiooni puudulikkuse tõttu peame oma PWM -funktsiooni lõpetama xtmrctr.h ja AXI Timer v2.0 LogiCORE IP tootejuhendi abil.

Samm 15: PWM-mooduli loomine- PWM-funktsiooni mähis (I)

Tagasi põhifaili "helloworld.c" juurde kaasake järgmised päisefailid:

16. etapp: PWM-mooduli loomine- PWM-funktsiooni pakkimine (II)

Määrake kahe AXI TImeri baasaadressid jaotises „xparameters.h”.

17. etapp: PWM-mooduli loomine- PWM-funktsiooni pakkimine (III)

Looge soovitud PWM -funktsioon.

Duty_val: teisendab kraadiväärtuse töötsükliks. PWM_Freq_Duty: määrake soovitud sagedus ja töötsükkel PWM -i genereerimiseks. Samuti tuleks määrata kellaaeg.

PWM_START: määrake PWM -registriaadress ja alustage PWM -i genereerimist.

PWM_STOP: määrake PWM -registriaadress ja lõpetage PWM -i genereerimine.

Ülejäänud demokood kuvatakse jaotises „helloworld.c” jaotises „Axis_2_PWM_SDK”

18. samm: PWM-mooduli ehitamine- käivitage see

1. Programmeerige FPGA SDK kaudu

- Ühendage Zybo Board USB -pordi kaudu arvutiga.

- Xilinxi tööriistad -> Programmeerige FPGA

2. Käivitage programm

Klõpsake ikooni „Käivita“ja rippmenüüst -> Käivita kui -> Käivita riistvaral

3. SDK terminal

- Avage SDK -terminal -> Ühenda jadapordiga -> OK

- Käivitage programm. Kui demokood töötab edukalt, peaksite nägema teksti „Initsialiseerimine tehtud!” SDK terminalis.

19. samm: videotöötluse voogesitus Digilent ZYBO -s OV7670 abil

Lisatud täielik arhiivifail.

Samm: täitke plokkskeem

See näitab projekti kõigi ühenduste ja IP -plokkide täielikku skeemi

Samm: ühendage OV7670 ZYBO -ga

Looge ühendus ov7670 mooduli ühendamiseks ZYBO Pmodidega

Andmed Pmod on Pmod D.

Kontroll Pmod on Pmod C

Lisaks ühendage PmodCON3 ja servod, nagu on kirjeldatud selle õpetuse esimeses pooles

22. samm: looge plokkide kujundus

Klõpsake Flow Navigatoris nuppu "Loo plokkide kujundus", seejärel vajutage OK.

23. toiming: lisage VHDL -failid OV7670 kaamera juhtimiseks ja jäädvustamiseks

Lisage projektile selle sammu juurde lisatud VHDL -failid

Samm: lisage piirangute fail

Lisage projektile lisatud piirangute fail.

Samm: lisage HLS IP jaoks IP Repo

Võtke lisatud Zip -fail ja pakkige see uude kausta, mis on sarnaselt nimega uues kataloogis (kaustas) nimega "HLS_repo".

Lisage oma projektile IP-hoidla, minnes IP-kataloogi ja paremklõpsake, valides "Lisa hoidla …"

Liikuge oma kataloogi "HLS_repo" ja valige see.

Valikuline: looge endale HLS videotöötlusplokk!

Samm: lisage moodulid ja IP

Lisage moodulid ov7670_axi_stream_capture, debounce ja ov7670_controller plokkskeemile, paremklõpsates taustal ja valides "Lisa moodul …"

Samamoodi lisage IP -d:

- HLS_Video_Track

- Video Frame Buffer Write

- Videokaadri puhverlugemine

- Video ajastamise kontroller

- AXI4-Stream videoväljundiks

- "Lõik" 3

- Pidev

- 2 AXI taimerist

Samm 27: IP -konfiguratsiooniseaded

Nagu piltidel näidatud

Samm: lisage ja konfigureerige PS IP -blokeering

Lisage plokkskeemile töötlemissüsteem ZYNQ7

muutke konfiguratsiooni:

-

PS-PL konfiguratsioon

-

HP

- Luba S HP 0

- Luba S HP 1

-

-

Kella konfiguratsioon

-

PL kangast kellad

- FCLK_0 sagedusel 100 MHz

- FCLK_1 sagedusel 25 MHz (väljundkell)

- FLCK_2 sagedusel 35 MHz (<= 50 MHz) (CameraClock)

-

Samm 29: 1. osa. PWM -mooduli ehitamine servomootoritele

Tooge axi_timer_0 pwm0 uude väljundporti pwm_Xaxis

Tooge axi_timer_1 pwm0 uude väljundporti pwm_Zaxis

30. samm: videosisendi külgühendused (esile tõstetud)

Ühendage videosisendipoolsed IP -plokid õigesti

(* need ühendused tuleks luua, valides ühenduse automatiseerimise ajal õiged valikud) "aclk" axi_stream_capture'ist läheb aadressile:

- ap_clk videokaadri puhver kirjutada

- ap_clk HLS videovoo töötlemise plokis

- *aclk AXI smartconnect IP -l videokaadri puhverist Kirjutage aadressile S_AXI_HP0

- *Aclk, mis vastab AXI Interconnect IP kanalitele HLS videotöötlusploki S_AXI kanalite ja videokaadri puhver jaoks, kirjutage PS -plokile S_AXI_HP0_ACLK

Videovoo signaal on lihtsalt järjestikku ühendatud võtteplokist Zynqi mäluliidesesse.

- Video läheb salvestusplokist HLS -i töötlusplokki.

- HLS -plokist töödeldud video läheb kaadripuhvri kirjutamisplokki.

- *Kaadripuhvri kirjutusplokk ühendub Zynq PS ploki HP0 liidesega.

- Püüdmisploki väljundist saadav m_axis_tuser signaal ühendatakse käsitsi nii HLS töötlusploki video_in_TUSER sisendsignaaliga kui ka samas plokis oleva ap_start signaaliga.

AXI videovoo protokoll kasutab signaali TUSER (tuser), et näidata video kaadri algust. AP_Start käsib HLS -plokil töötlemist alustada. Seega kasutame kasutajat, et käivitada HLS -plokk, et töödelda iga kaadrit sellisena, nagu see on Siini ühe signaali ühendamisel ja sel viisil eraldamisel tuleb see ühendada ka ülejäänud bussi tavalise lõpp -punktiga. Vivado eeldab, et kui ühendate signaali käsitsi, soovite lahti ühendada selle, millega see tavaliselt ühenduks.

IP -plokkide konfiguratsiooniseaded:

Videokaadri puhver kirjutage:

Videoformaadid: RGB8

1 näidis kella kohta Maksimaalsed veerud: 1280 (> = 640) Maksimaalsed read: 960 (> = 480) Maksimaalne andmete laius: 8

Samm: ühendused OV7670 -ga

Blokil ov7670_axi_stream_capture

- Tehke kõik sisendid väliseks (paremklõpsake tihvti ja valige menüüst või vasakklõps-> ctrl+T)

- Jätke nimed nii, nagu need on

Kontrolleriplokil ov7670_

- Muutke kõik plokiväljundid väliseks

- Nimetage port config_finished ümber led0 -ks

- ühendage clk CameraClockiga (<= 50MHz) (FCLK_2)

Tagasilöögiplokil

- ühendage nupp1 sisend välise sisendpordiga btn0

- ühendage out1 ov7670_controller IP -ploki uuesti saatmisliiniga

- ühendage button2 sisend välise sisendpordiga btn3

- ühendage out2n video jäädvustamise kella domeeni protsessori süsteemi lähtestamise IP sisendiga ext_reset_in. (*Seda tuleb võib -olla teha pärast seda, kui IP on loodud*)

- ühendage clk CameraClockiga (<= 50MHz) (FCLK_2)

Samm 32: Ühendused video väljundis

Ühendused plokkidele Video Timing Controller (VTC), AXI4-Stream to Video Out ja viilud

- Kasutage vid_io_out_clk ja VTC clk jaoks 25MHz kella (FCLK_1)

- Kasutage 100MHz kella (FCLK_0) AXI4-Streami videoväljundiks

- vtiming_out kuni vtiming_in

- Videokaadri puhver Loe m_axis_video läheb AXI4-Streami videoväljundisse video_in

- vtg_ce läheb gen_clken

- Seosta VTC ummistunud, aklken, vid_io_out_ce konstantse doutiga [0: 0]

- Tooge vid_hsync ja vid_vsync vastavalt välistele väljundportidele vga_hs ja vga_vs. (pole pildil)

Viilud:

-

Viilud tuleb seadistada nii, nagu on näidatud lisatud piltidel

- nimetage plokid ümber viiludeks -punasteks, viilude_rohelisteks ja viilude_sinisteks

- häälestusviilude vahemikud, nagu on näidatud piltidel ploki nime järgi

- ühendage iga viilu väljund välise pordi väljundiga, nagu pildil näidatud.

- vid_data [23: 0] ühendub iga viilu sisenditega (Din [23: 0])

Samm 33: käivitage plokkide ja ühenduse automatiseerimine

Käivitage plokkide automatiseerimine, et ühendada asjad ZYNQ7 PS plokist. Nagu pildilt näha.

Käivitage ühenduse automaatika, et luua kogu ühendus -IP. Pöörake tähelepanu iga pildi kõikidele võimalustele.

Tagasilöögiplokil ühendage out2n videosalvestuskella domeeni protsessorisüsteemi lähtestamisega ext_reset_in.

Samm: looge HDL -pakend

Looge oma plokkide jaoks HDL -pakend.

Seadke see ülemiseks mooduliks.

Samm: looge bitivoo, eksportige riistvara SDK -sse, käivitage SDK Vivadost

Lisage eksportimisel kindlasti ka bitivool.

Bitivoo genereerimine võib võtta väga kaua aega.

Seejärel käivitage SDK

36. samm: SDK (FreeRTOS puudub)

See versioon teeb kõike ilma FreeRTOS -i kasutamata, kondenseerides koodi kenasti.

Looge riistvara disainil põhinev eraldiseisev BSP. Vaikevalikud peaksid olema korras. Veenduge, et BSP -allikad on loodud.

Looge rakendus, nagu on näidatud pildil. (tühi rakendus)

Kustutage automaatselt loodud peamine ja importige manustatud failid.

37. samm: FreeRTOS -i juurutamine

See versioon kasutab FreeRTOS -i. Looge FreeRTOS901 BSP riistvara disaini põhjal. Vaikevalikud peaksid olema korras. Veenduge, et BSP -allikad on loodud.

Looge rakendus, nagu on näidatud pildil. (tühi rakendus)

Kustutage automaatselt loodud peamine ja importige manustatud failid.

Samm 38: Kasutusjuhised

Selle projekti käivitamine on natuke keeruline. Järgige samme järjekorras.

Veenduge, et teie ZYBO ei laadiks sisselülitamisel midagi ise. See tähendab, et Valmis LED ei peaks süttima. Üks võimalus seda teha on seada alglaadimisallika hüppaja asendisse JTAG.

Avage projekt (FreeRTOS või mitte), mida soovite SDK -st programmeerida

- Lülitage ZYBO sisse. Valmis LED ei tohiks süttida.

- Programmeerige FPGA bitifailiga. Valmis LED peaks süttima. Led0 ei tohiks süttida.

- Käivitage kood (kui te seda teete, pidage meeles, et lähete alguspunktist mööda).

Sel hetkel peaksite oma VGA -ekraanile väljundi saama.

Taaskäivitamiseks (kui see vigastab või mida iganes): puudutage kiiresti nuppu PS-SRST või lülitage ZYBO välja ja uuesti sisse. Jätkake sammust 2.

Protsessori peatamine siluriga viib kaamera liikumise asemel asendisse. Videovoog jätkub niikuinii.

Samm 39: Viited ja lingid

Xilinxi juhendid ja dokumentatsioon:

- PG044 - AXI -Stream videoväljundiks

- PG278 - Videokaadri puhver lugemiseks/kirjutamiseks

Muud lingid:

- Lauri blogi - VDMA sisend

- Lauri blogi - OV7670 VGA väljundisse, kasutades BRAM -i

- Hamsterworks wiki, autor Mike Fields, OV7670 koodi algallikas

- Andmeleht, mis näitab põhilisi ajastuspiiranguid

Soovitan:

Akvaariumi disain koos põhiparameetrite automatiseeritud juhtimisega: 4 sammu (piltidega)

Akvaariumi disain koos põhiparameetrite automatiseeritud juhtimisega: Sissejuhatus Täna on mereakvaariumi hooldus kättesaadav igale akvaaristile. Akvaariumi omandamise probleem pole keeruline. Kuid elanike täielikuks elutoeks, kaitseks tehniliste rikete eest, lihtsaks ja kiireks hoolduseks ja hoolduseks

Odav 3D 3D -kaamera kaamera Androidile: 7 sammu (piltidega)

Odav 3D FPV kaamera Androidile: FPV on päris lahe asi. Ja 3D -s oleks see veelgi parem. Kolmas mõõde ei ole suurtel vahemaadel eriti mõttekas, kuid siseruumides asuva mikrokvadropteri jaoks on see ideaalne. Nii et ma vaatasin turgu. Kuid minu leitud kaamerad olid ka tema

CCTV kaamera koos sõlmega MCU + vana sülearvuti kaamera moodul (koos ja ilma Blynk'i kasutamiseta): 5 sammu

CCTV kaamera koos NodeMCU + vana sülearvuti kaamera mooduliga (koos ja ilma Blynk'i kasutamiseta): Tere poisid! Selles juhendis näitan teile, kuidas kasutasin vana sülearvuti kaamera moodulit ja sõlme MCU, et teha midagi sarnast CCTV -ga

Vikerkaare torn koos rakenduse juhtimisega: 6 sammu (piltidega)

Vikerkaare torn koos rakenduse juhtimisega: vikerkaare torn on rakenduse juhitav ümbritsev valgus. Kasutasin valgusallikana WS2812 LED -riba ja tulede juhtimiseks ESP8266 moodulit. Küljed on valmistatud valgest akrüülklaasist, mis on suurepärane materjal valguse hajutamiseks. Rakendusega saate

PhotonLamp - WS2812b varustatud disainlamp koos MQTT juhtimisega: 5 sammu (piltidega)

PhotonLamp - WS2812b varustatud disainlamp koos MQTT -juhtimisega: mitu aastat tagasi ostsime disainlambi, millel oli sigari kujuga lambivari ja mis oli valmistatud piimaklaasist. Meile meeldis varju eriline disain ja lambi üldine välimus. Aga ma pole rahuga päris rahul olnud