Sisukord:

- Samm: mis on Vivado HLS?

- 2. samm: HLS videoteek

- 3. samm: sünteesimine

- Samm 4: Versioonide ja muu teave ekspordiks

- Samm: eksportimine Vivado IP -teeki

- 6. samm: süntees ja ekspordi analüüs

- Samm: IP -teegi lisamine Vivadosse

- 8. samm: uuendage

- 9. samm: lisateave ja teave

- 10. samm: väljund ja sisend

- Samm 11: AXI registri liides

- 12. samm: andmevoo pragma

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:50.

- Viimati modifitseeritud 2025-01-23 14:40.

Kas olete kunagi tahtnud videot reaalajas töödelda ilma palju latentsust lisamata või manussüsteemis? Selleks kasutatakse mõnikord FPGA -sid (Field Programmable Gate Arrays); videotöötlusalgoritmide kirjutamine riistvara spetsifikatsiooni keeltes nagu VHDL või Verilog on aga parimal juhul masendav. Sisestage Vivado HLS, Xilinxi tööriist, mis võimaldab teil programmeerida C ++ keskkonnas ja genereerida sellest riistvara spetsifikatsiooni keelekoodi.

Nõutavad tarkvara:

- Vivado HLS

- Vivado

- (Kui kasutate AXI -registreid) Vivado SDK

(Valikuline) Laadige Xilinxi tehtud näited alla siit:

Xilinx HLS video näited

Samm: mis on Vivado HLS?

Vivado HLS on tööriist, mida kasutatakse c ++ sarnase koodi muutmiseks riistvarastruktuurideks, mida saab rakendada FPGA -l. See sisaldab IDE -d selle arenduse tegemiseks. Kui olete HLS -i koodi väljatöötamise lõpetanud, saate oma loodud IP -vormingu eksportida kasutamiseks koos Vivadoga.

Laadige alla lisatud failid ja asetage need projekti loomise koha lähedale. (nimetage need ümber "top.cpp" ja "top.h", kui neil on randomiseeritud nimi)

2. samm: HLS videoteek

HLS -i videoteegis on selles dokumendis viitedisainiga dokumentatsioon: XAPP1167 Teine hea ressurss on Xilinxi Wiki leht selle kohta.

Käivitage Vivado HLS.

Loo uus projekt.

Võtke eelmises etapis alla laaditud failid ja lisage need lähtefailidena. (Märkus: faile ei kopeerita projekti, vaid need jäävad sinna, kus need on)

Seejärel kasutage ülemise funktsiooni valimiseks nuppu Sirvi.

Järgmisel lehel valige Xilinxi osa, mida kasutate.

3. samm: sünteesimine

Lahendus => Käivita C süntees => Aktiivne lahendus

~ 227,218 sekundi pärast tuleks see ära teha. (Märkus: teie tegelik sünteesiaeg varieerub sõltuvalt paljudest teguritest)

Samm 4: Versioonide ja muu teave ekspordiks

Versiooninumbrid suhtlevad Vivadoga, et saaksite kujunduses IP -d värskendada. Kui tegemist on väiksema versioonimuudatusega, saab seda teha, samas kui peamised versioonimuudatused nõuavad uue ploki käsitsi lisamist ja vana eemaldamist. Kui teie liidesed pole muutunud ja versiooniuuendus on väike, saab värskenduse teha Seda tehakse automaatselt automaatselt, vajutades värskendamise IP -nuppu. IP -aadressi oleku vaatamiseks saate käivitada "report_ip_status" Vivado tcl konsoolis.

Määrake versiooninumbrid ja muu teave jaotises Lahendus => Lahenduse seaded…

Teise võimalusena saab neid seadeid eksportimise ajal määrata.

Samm: eksportimine Vivado IP -teeki

Lahendus => Ekspordi RTL

Kui te ei määranud IP -teegi üksikasju eelmises etapis, saate seda teha kohe.

6. samm: süntees ja ekspordi analüüs

Sellel ekraanil näeme meie eksporditud mooduli statistikat, mis näitab, et see vastab meie kellaajale 10ns (100MHz) ja kui palju igast ressursist see kasutab.

Selle, meie sünteesiaruande ja andmevoo analüüsi kombinatsiooni abil näeme, et selleks kulub 317338 taktsüklit * 10ns kellaaega * 14 torujuhtme etappi = 0,04442732 sekundit. See tähendab, et meie pilditöötluse lisatud latentsusaeg on alla kahekümnendiku sekundist (kui see on suunatud 100 MHz sagedusele).

Samm: IP -teegi lisamine Vivadosse

Sünteesitud IP -ploki kasutamiseks peate selle Vivadosse lisama.

Vivados lisage oma projektile IP-hoidla, minnes IP-kataloogi ja paremklõpsake, valides "Lisa hoidla …"

Liikuge oma Vivado HLS projektikataloogi ja valige oma lahenduste kataloog.

See peaks teatama leitud IP -st.

8. samm: uuendage

Mõnikord peate pärast Vivado kujundusse lisamist oma HLS -plokki muutma.

Selleks saate teha muudatusi ning uuesti sünteesida ja eksportida kõrgema versiooninumbriga IP -d (vt üksikasju eelmises etapis peamiste/väiksemate versiooninumbrite muudatuste kohta).

Pärast uue versiooni eksportimise muutmist värskendage oma IP -hoidlaid Vivados. Seda saab teha siis, kui Vivado märkab, et IP on hoidlas muutunud, või aktiveeritakse see käsitsi. (Pange tähele, kui värskendate oma IP -hoidlaid pärast alustamist, kuid enne eksportimise lõppu HLS -is, pole IP -d ajutiselt olemas, oodake selle lõppu ja värskendage uuesti.)

Sel hetkel peaks ilmuma aken, kus on teave selle kohta, et IP -d on kettal muudetud, ja annab teile võimaluse seda värskendada nupuga "Uuenda valitud". Kui muudatus oli väike versioonimuutus ja ükski liides ei muutunud, siis selle nupu vajutamine asendab vana IP automaatselt uuega, vastasel juhul võib olla vaja rohkem tööd teha.

9. samm: lisateave ja teave

Järgmised sammud annavad lisateavet selle kohta, kuidas HLS -i süntees toimib ja mida saate sellega teha.

HLS -i sünteesitud IP -plokki kasutava projekti näite leiate sellest juhendist.

10. samm: väljund ja sisend

Lõpliku IP -ploki väljundid ja sisendid määratakse analüüsi põhjal, mida süntesaator teeb andmevoo ülemisest funktsioonist sisse ja välja.

Sarnaselt VHDL -i või verilogiga võimaldab HLS määrata IP -de vaheliste ühenduste üksikasju. Need read on selle näited:

tühine pildi_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE teljeport = video_in kimbu = INPUT_STREAM #pragma HLS INTERFACE teljeport = video_out kimp = OUTPUT_STREAM #pragma HLS INTERFACE s_axilite port = x kimbu = CONTROL_BUS offset = 0x14 #pragma y_xing interface

Näete, kuidas need direktiivid mõjutavad IP -plokil eksponeeritud porte.

Samm 11: AXI registri liides

Selleks, et sisestada/väljastada oma IP -plokki PS -i, on hea viis seda teha AXI -liidese kaudu.

Saate selle määrata oma HLS -koodis, sealhulgas nihked, mida hiljem väärtusele juurde pääsemiseks kasutada.

tühine pildi_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE s_axilite port = x kimp = CONTROL_BUS offset = 0x14

#pragma HLS INTERFACE s_axilite port = y kimbu = CONTROL_BUS offset = 0x1C #pragma HLS andmevoog

x = 42;

y = 0xDEADBEEF; }

Kui olete Vivados korralikult ühendatud, pääsete väärtustele juurde, kasutades seda koodi Vivado SDK -s:

#include "parameetrid.h"

#define xregoff 0x14 #define yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff); y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff);

Selle tulemuseks on 42 x ja 0xdeadbeef y

12. samm: andmevoo pragma

#Pragma DATAFLOW sees muutub koodi rakendamise viis tavalisest C ++ -st. Kood on konveieeritud nii, et kõik juhised töötavad andmete erinevates osades kogu aeg (mõelge sellele nagu tehase kokkupanekuliinile, iga jaam töötab pidevalt, täites üht funktsiooni ja edastades selle järgmisele jaamale)

pildilt näete, et iga direktiiv

Vaatamata sellele, et need näivad olevat tavalised muutujad, rakendatakse img -objekte käskude vahel väikeste puhvritena. Kujutise kasutamine funktsiooni sisendina "tarbib" seda ja muudab selle enam kasutuskõlbmatuks. (Seega on vaja käske dubleerida)

Soovitan:

Minu esimene süntees: 29 sammu (piltidega)

Minu esimene süntesaator: Lapse süntesaator tekkis, kui ma istusin küürus süntesaatorijuhtmete sassis. Mu sõber Oliver tuli kohale, hindas olukorda ja ütles: "Teate, et teil on õnnestunud teha maailma kõige keerulisem laste mänguasi." Kuigi minu esialgne r

Phono -Chronoxyle - 360 kraadi süntees: 3 sammu (piltidega)

Phono -Chronoxyle - 360 kraadi süntees: Pariisist pärit Julien Signolet'i skulptor ja muusik Mathias Durand pöördusid minu poole Nuit Blanche 2019 jaoks Pariisis Parc Floral interaktiivse heliinstallatsiooni jaoks. Installatsioon oleks väljas ja ma ei oleks selle ajal kohal sees

Sigarikarbi süntees: 14 sammu (piltidega)

Cigar Box Synth: Siin on minu viimane süntesaator, mis on valmistatud taimerist 555 ja 556 koos 4017 ic -ga. Paar kuud tagasi oleks selline ehitamine olnud minu oskuste tasemest väljumine. Kuid viimastel kuudel olen parema tulemuse nimel kokku pannud mõned lihtsad süntesaatorid

Retro kõne süntees. Osa: 12 asjade Interneti, koduautomaatika: 12 sammu (piltidega)

Retro kõne süntees. Osa: 12 IoT, koduautomaatika: see artikkel on koduautomaatika seeria 12. käsikiri, mis dokumenteerib, kuidas luua ja integreerida IoT Retro kõnesünteesiseade olemasolevasse koduautomaatikasüsteemi, sealhulgas kõik vajalikud tarkvarafunktsioonid, mis võimaldavad t

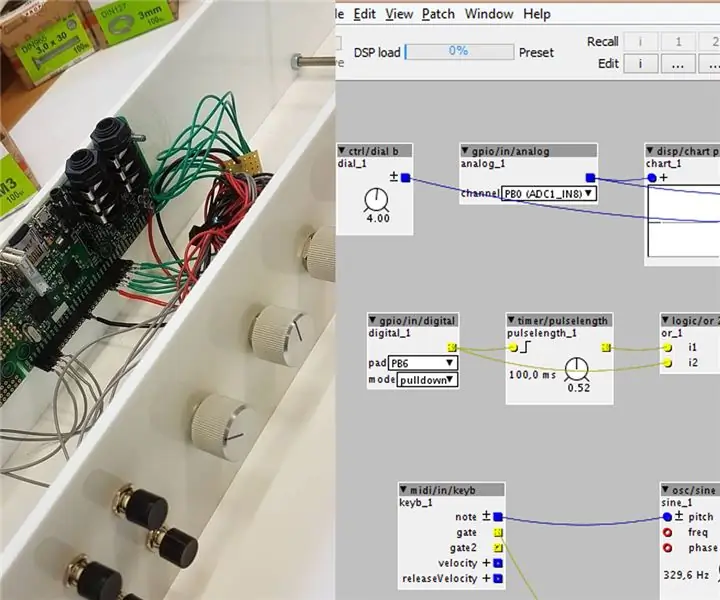

Lihtne süntees - Axoloti kontroller ja tarkvara tutvustus: 3 sammu

Lihtne süntees - Axoloti kontroller ja tarkvara sissejuhatus: Axoloti on mitmekülgne heliplaat, mis on programmeeritav väga sarnaselt Arduinoga, just koos sõlmepõhise heli arenduskeskkonnaga. Sealt programmeeritud plaastrid laaditakse pärast lõpetamist üles ja seejärel käivitatakse tahvlil iseseisvalt. Sellel on mitu