Sisukord:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:46.

- Viimati modifitseeritud 2025-01-23 14:40.

JDM on populaarne PIC -programmeerija, kuna see kasutab jadaporti, minimaalselt komponente ega vaja toiteallikat. Kuid seal on segadust, kuna võrgus on palju programmeerijate variatsioone, millised neist milliste PIC -idega töötavad? Selles "juhendatavas" panime JDM -i proovile ja ma demonstreerin, kuidas vooluringi simuleerida Spice'i abil, mis vastab kõigile teie küsimustele!

Tarvikud

LTspice, mille saate alla laadida analoogseadmetest siit.

Siin on vaja ka JDM -ahela faile.

Samm: jadapordi nõuded

JDM nõuab jadaporti, mis vastab EIA232 spetsifikatsioonile, ideaaljuhul +12/-12 pingetasemega.

Vastavalt Texas Instruments Line Driver MC1488 andmelehele (joonis 3)

Väljundtakistus = 4V/8mA = 500 oomi.

Lühisvoolu piir = 12 mV, ilma ajapiiranguta - kiip ei kahjusta.

Liini vastuvõtja sisendtakistus on soovitatav 3 kuni 7 k oomi.

Vanemate lauaarvutite jadapordid kasutavad sellele nõudele vastavat +12v/-12V.

Uuemate sülearvutite jadapordid kasutavad madalamat pinget. JDM võib töötada või mitte - vastus on keerulisem.

2. samm: PIC -i programmeerimisnõuded

Teave PIC -i programmeerimisnõuete kohta saadakse Microchipilt. Ülaltoodud on tüüpilise seadme jaoks.

3. samm: JDM -i spetsifikatsioon

Kas JDM -i algne veebisait on aja jooksul udusse kadunud? See jätab meid arvama, mida disainer algselt spetsifikatsiooni jaoks kavandas.

- Esitage VDD = 5 V ja kuni IDD = maksimaalselt 2 mA (pistikupesa versiooni puhul)

- Andke VHH = 13V ja kuni IHH = 0,2 mA.

- MCLR Tõusuaeg tVHHR = max 1uS.

- ICSP versioon peab suutma tõsta MCLR-i madalalt 22k tõmbe vastu sihtmärki.

4. samm: ahela kirjeldus

Joonis JDM1 põhineb PICPgm veebisaidilt võetud “standardsel” JDM -ahelal. See on programmeerija “PIC in Socket”, kus PIC võtab voolu TX- ja RTS -tihvtidelt. Algsest skeemist oli raske aru saada, nii et olen selle uuesti joonistanud, kasutades ülalt alla tavalist vooluhulka. Ja olen lisanud ehitamise ja katsetamise ajal vajalikud LED -indikaatorid “RESET”, “PROG” ja “RTS”. Loodetavasti ei mõjuta need käitumist kahjulikult.

Vooluahela projekteerimise tavapärane tava on kõigile ühine, kuid JDM -i põhijooneks on see, et jadapordi maandus (GND) on ühendatud VDD -ga. See tekitab segadust, kuna jadapordi signaale mõõdetakse GND, PIC -signaalide suhtes loogilise maanduse (VSS) suhtes.

Kui TX tõuseb kõrgele, käitub Q1 kahe ettepoole kallutatud dioodina. (Q1 kollektor ei ole tagurpidi kallutatud nagu tavalise transistori töö korral). Q1 kollektor laeb C2, mille Zener (D3) kinnitab VDD+8V pingele. Q1 emitter edastab 13V to MCLR programmeerimis-/kontrollimisrežiimi jaoks.

Kui TX langeb madalale, laetakse kondensaator C3 läbi D1 ja VSS kinnitatakse Zeneriga (D5) VDD-5V külge. Samuti kinnitatakse TX (VSS-0.6) D1 abil. Q1 on välja lülitatud, C1 hoiab järgmise programmipulsi eest tasu. D2 kinnitab MCLR -i 0V juures, nii et PIC on nüüd lähtestatud.

Kui RTS on kõrge, edastatakse kell PGC -le. D4 klamber PGC kõrge VDD loogikaga. Kui RTS on madal, laetakse kondensaator C3 läbi D6 ja VSS kinnitatakse Zeneriga (D5) VDD-5V. D6 kinnitab PGC VSS -i või loogikaga 0.

Programmeerimise ajal loetakse DTR -ile saadetud andmed PGD -lt, mille PIC konfigureerib sisendiks. Kui DTR on kõrge, toimib Q2 „emitteri järgijana” ja PGD pinge on umbes (VDD-0,6) või loogika 1. Kui DTR on madal, toimib Q2 halva transistorina (emitter ja kollektori tihvtid on tagurpidi). Q2 tõmbab PGD madalaks, mille D7 kinnitab VSS -i või loogika 0 juures.

Kontrollimise ajal konfigureerib PIC PGD väljundina jadaporti andmete saatmiseks. DTR peab olema kõrge ja andmed loetakse CTS -is. Kui PGD väljund on kõrge, on Q2 välja lülitatud, CTS = DTR = +12V. Kui PGD väljund on madal, on Q2 sisse lülitatud. Q2 kollektor tõmbab DTR -st voolu (12V+5V)/(1k+1k5) = 7mA ja tõmbab CTS -i madalale VSS -i.

Samm: valmistuge simulatsiooniks

Laadige alla LT vürts, salvestage ja avage siin esitatud ahelafailid (*.asc). Vooluahela simuleerimiseks peame andma sellele mõned sisendid ja seejärel "jälgima" väljundeid. V1, V2 V3 simuleerivad 12V jadaporti väljundtakistusega R11, R12, R13.

- V1 genereerib TX -l 2 programmimpulssi vahemikus 0,5 ms kuni 4,5 ms

- V2 genereerib DTR -i andmeimpulsside vaheaja 1,5 kuni 4,5 ms

- V3 genereerib RTS -i kellaimpulsside vahemiku 0,5 kuni 3,5 ms

Kõik komponendid V4, X1, R15 ja R16 on osa simulatsioonist.

- V4 genereerib andmete kontrollimiseks 2 impulsi vahemikus 2,5 kuni 4,5 ms.

- Jumper X1 simuleerib PGD väljundit.

- R15, R16 simuleerivad PIC -i „laadimist” VDD -le ja MCLR -ile.

6. samm: ICSP muutmine

Joonis JDM3 näitab ahela programmeerimise versiooni. Muudatused originaalist on

- Asendage ZIF -pesa ICSP -pistikuga.

- PIC töötab nüüd toiteallikana sihtvooluringi (V5).

- Eemaldage 5V zener (D5).

- Väike 100 pF kondensaator (C4) liigutatakse sihtringi PIC kõrval.

- LED -id võtavad võimaluse korral trükkplaadilt toite.

- Sihtlülitusel on vaja MCLR-i tõmbetakistit (R10) ja dioodi (D10).

- HOIATUS. Sihtplaadil peab olema ujuv toide, ideaaljuhul aku.

- Ärge ühendage sihtmaandust (VSS) arvuti/arvuti maandusega, ühendades samal ajal JDM -iga muid arvutiporte.

Pärast JDM1 simuleerimist ilmnes C2 pika laadimisaja probleem. Pärast Fruttenboeli lugemist ilmneb, et C2 ja Q1 lisati originaalile modifikatsioonina. Ma ei suuda mõelda, mida C2 ja Q1 on mõeldud peale probleemide tekitamise. Nii pöördume JDM4 puhul tagasi Fruttenboeli vanema disaini juurde, mis on lihtne ja arusaadav. D1 ja D3/LED2 klamber MCLR VSS ja VDD+8V vahel. R1 väärtus on vähendatud 3 k3 -ni, mis on piisav LED2 valgustamiseks 12 V juures.

JDM4 on loodud töötama ka nõrgemate jadaportidega. Kui TX tõuseb kõrgele (+9V), on TX vooluallikas = (9-8)/(1k +3k3) = 0,2 mA, mis on piisav, et tõsta MCLR-i kõrgeks, ehkki ebapiisavaks LED2 valgustamiseks. Kui TX läheb madalaks (umbes -7V), siis TX vool vajub = (9-7)/1k = 2mA. LED1 vool = (7-2 LED-i jaoks)/(2k7) = 1,8 mA. MCLR tõmbevool = 7-5,5/3k3 = 0,5 mA.

Seda vooluahelat on samuti testitud (JDM5 simulatsioon), et näha, mis juhtub vähemalt +/- 7V jadaportidega, kus VHH = 13V püsimiseks pole piisavalt pinget. Nüüd ilmneb C1 eesmärk, C1 loob MCLR -ile lühikese +ve -tõuke, 33x piigi TX tõusvas servas, piisavalt kaua, et PIC saaks programmeerimisrežiimi siseneda. Kuid eemaldage hüppaja X2 (keelake LED1), kuna vool ei ole piisav MCLR -i madalaks tõmbamiseks ja LED1 koos valgustamiseks. Kui TX langeb, on TX-voolu vajumine = (7V-5,5 V)/(1k+3k3) = 0,3 mA, mis on piisav, et tõmmata MCLR-i madalale tõmbejõu R10 vastu.

Samm 7: Simulatsiooni tulemused

Graafiliste failide vaatamiseks on parem paremklõps allolevatel linkidel ja seejärel valida "Ava link uuel vahelehel"

Simulatsioon 1: MCLR, VSS ja RTS jälg algse JDM1 jaoks. Vahetult ilmnevad tähelepanekud 1, 2 ja 3.

Simulatsioon 2: MCLR ja VSS ning modifitseeritud JDM2 RTS jälg, mis parandab varasemad probleemid.

Simulatsioon 3: PGD, VSS ja PGC jälgimine programmirežiimis andmete saatmiseks JDM2 jaoks. Vaatlus 4 3,5 mS juures.

Simulatsioon 4: PGD, VSS ja CTS jälg JDM2 jaoks kontrollimisrežiimis (hüppaja X1 sisestatud). Okei

Simulatsioon 5: MCLR, VSS, PGD ja PGC jälg JDM3 jaoks. ICSP, kasutades vooluahelat, saab lahendada palju probleeme.

Simulatsioon 6: MCLR, VSS, PGD ja PGC jälg JDM4 jaoks +/- 9V jadapordiga. MCLR tõuseb kohe, täiesti töökorras.

Simulatsioon 7: MCLR, VSS ja TX jälg JDM5 jaoks, eemaldades +/- 7V jadapordi ja hüppaja X2. C1 tekitab MCLR tõusva serva +ve tõusu (piigi), mis on peaaegu piisav, et tõsta MCLR üle TX 13 V -ni.

8. samm: Järeldused

Spice oskab tõesti hästi vooluringi toimimise “varjatud saladusi” paljastada. Ilmselt JDM -ahel töötab ja ühildub paljude PIC -kiipidega, kuid järgmised tähelepanekud näitavad võimalikke piiranguid/ühilduvusprobleeme/tõrkeid?

- MCLR -i pikk tõusuaeg, samal ajal kui C2 laeb VPP -le TX esimesel impulsil. Ei vasta spetsifikatsioonile 3.

- Jadaport laadib C2, kui TX tõuseb kõrgele ja RTS väheneb. Kuid RTS -l on ka C3 laadimine. Kui mõlemad toimuvad samal ajal, tekitab see RTS -ile suurema koormuse, järelikult kaotab C3 laengu (VSS tõuseb) simulatsioonil 2 ms. Ei vasta spetsifikatsioonile 1.

- C3 kaotab laengu (VSS hakkab tõusma) pärast kellaimpulsside peatumist 3,5 ms juures.

- Mis on C2 eesmärk, kas seda on üldse vaja?

Lahendused

- Eeldatavasti kasutab PICPgm tarkvara "tööringi". See peab rakendama C2 -le eellaadimiseks pika TX -impulsi, seejärel sisenema programmeerimisrežiimi alles pärast teist TX -impulsi? Simulatsiooni jaoks vähendasin C2 väärtust 1uF -ni, et tõustaks 1 ms. Pole ideaalne lahendus.

- Jagage C2 ja C3, nii et need laadivad iseseisvalt. Üks väike muudatus JDM2, C2 on viidatud GND -le VSS -i asemel.

- Lahendas JDM3. ICSP on palju usaldusväärsem, kuna PIC saab toite sihtmärgiahelast.

- JDM4 lahendab probleemi 1. See on lihtne disain, mis kõrvaldab C2 täielikult.

Samm: ja lõpuks

Pudingu tõestuseks on söömine. See JDM töötab, nii et jätkake selle kasutamist.

Ja minu soovitused on järgmised:

- kasutage JDM2 pistikupesade programmeerimiseks ja 12 V jadaportide jaoks,

- kasutage JDM4 ICSP programmeerija ja jadaportide jaoks üle +/- 9V,

- kasutage JDM4 ja eemaldage hüppaja X2, kui jadaport on üle +/- 7V.

Viited:

Analog Devices LT vürts

picpgm

Fruttenboel

Jälgige rohkem PIC-projekte kaval nurgas

Soovitan:

Elegoo Super käivitatud komplekti Uno R3 ülevaade: 4 sammu

Elegoo Super käivitatud komplekt Uno R3 ülevaade: paar päeva tagasi saatis Elegoo mulle selle Super Stardikomplekti testimiseks. Niisiis, vaatame, mis on sees. Selle kompaktse korpuse avamisel näeme palju asju. Kaanel on indeks kõigi komponentidega. Meie sees on tänukaart, kus on kõik

KS-Garden: ülevaade: 9 sammu

KS-Garden: Ülevaade: KS-Gardenit saab kasutada aia/kasvuhoonetaimede niisutamiseks/õhutamiseks/tagaaias valgustamiseks või siseruumides kasvatamiseks kasti (modulaarne disain) KS-Garden süsteem koosneb peamiselt järgmistest moodulitest: süsteemikarp - Relais ja toiteplokk

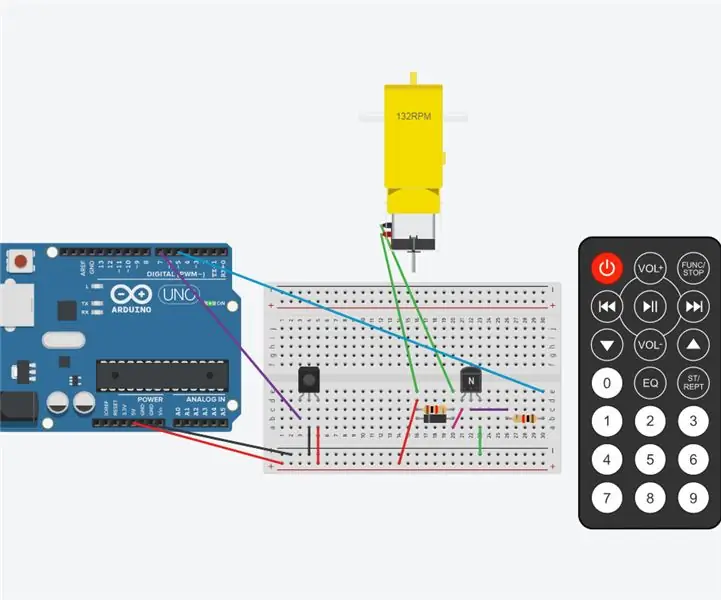

Transistoriga juhitav mootor kaugjuhtimispuldiga; Ahela ülevaade: 9 sammu

Transistoriga juhitav mootor kaugjuhtimispuldiga; Ahela ülevaade: see vooluahel on puldiga transistoriga juhitav mootor. Kaugjuhtimispult lülitab toite sisse. Transistor lülitab mootori sisse. Programmi kood suurendab mootori kiirust ja seejärel vähendage mootori pöörlemiskiirust nullini

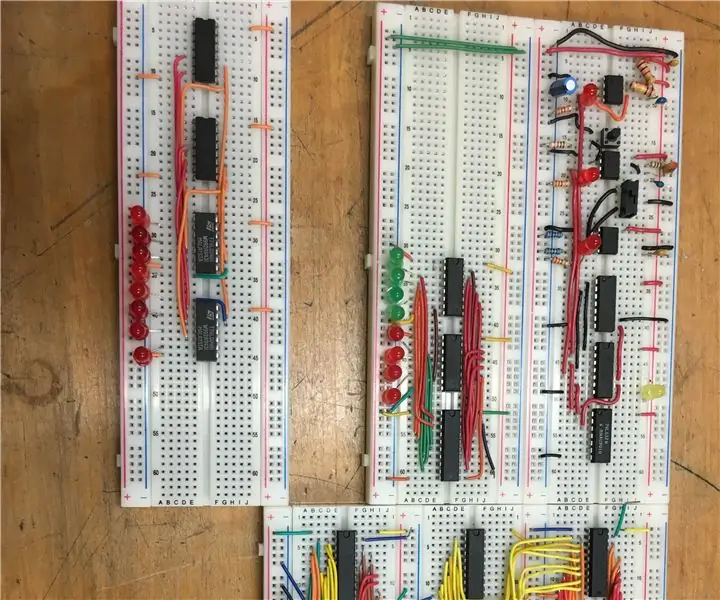

8-bitine arvuti leivaplaadil Ülevaade: 3 sammu

8-bitine arvuti leivaplaadil Ülevaade: Selle projekti eesmärk oli paremini mõista arvuti arhitektuuri, riistvara disaini ja koostetaseme keeli. Kuna olin juunior ülikoolis ja õppis arvutitehnikat, olin hiljuti läbinud elektroonika, laborite ja

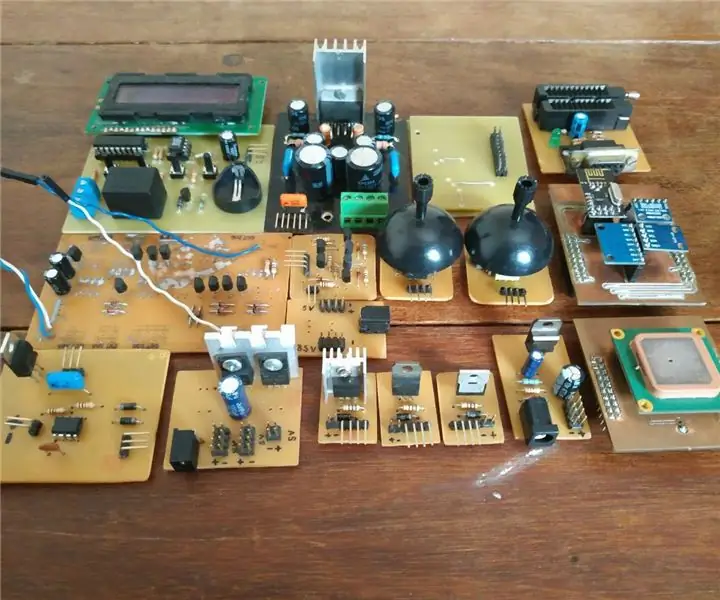

PCB projekteerimise ja söövitamise ülevaade: 5 sammu

PCB projekteerimise ja söövitamise ülevaade: PCB -de kavandamiseks ja söövitamiseks on mitmeid viise, alates kõige lihtsamatest kuni kõige keerukamateni. Vahepeal on lihtne segadusse sattuda, milline neist valida, milline neist sobib kõige paremini teie vajadustega. Selleks, et selgitada mõningaid küsimusi, näiteks